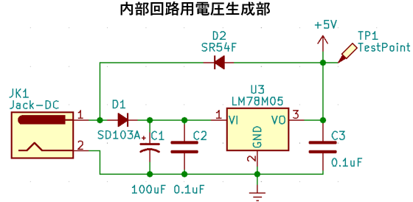

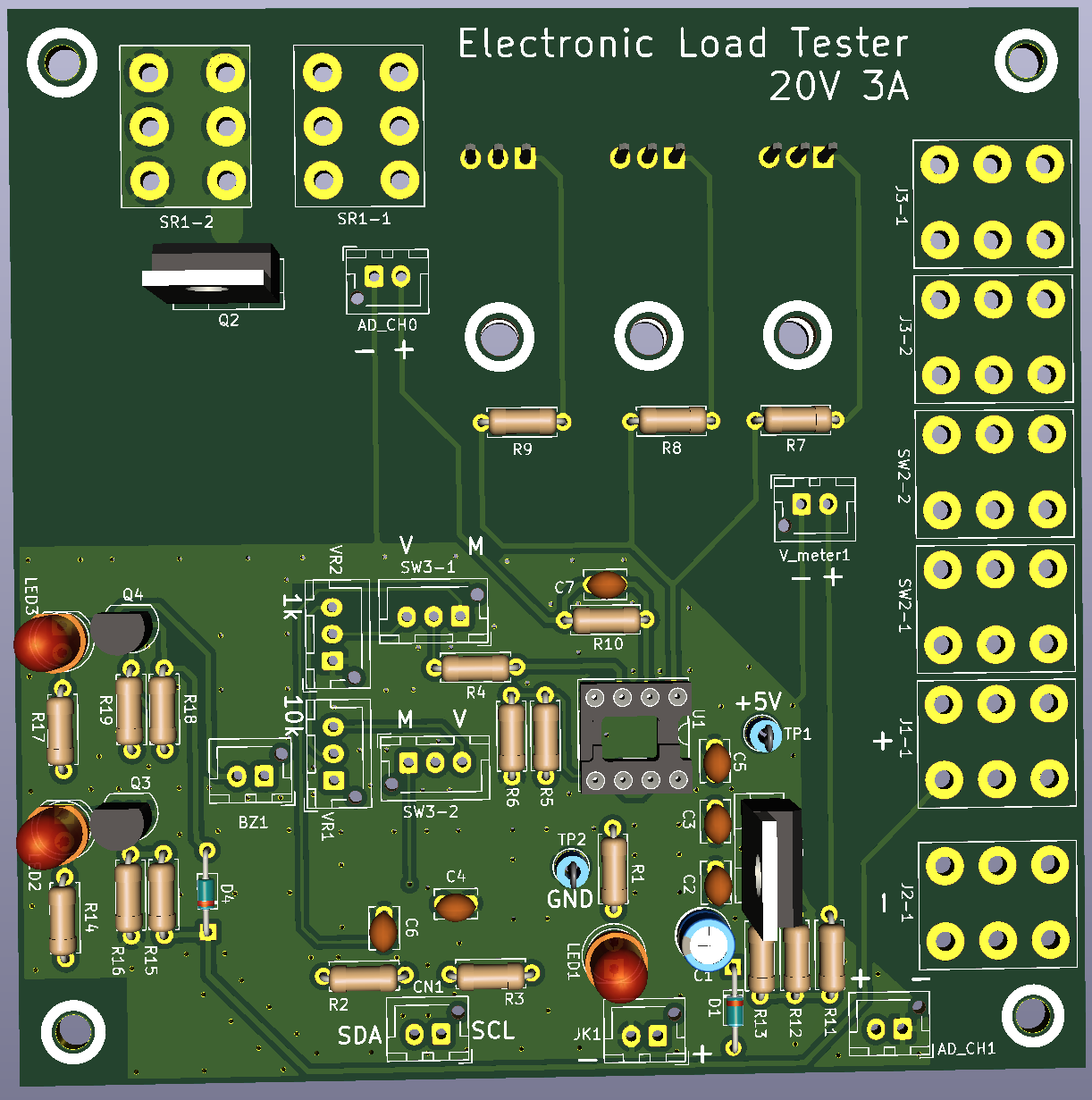

【回路図】

回路図 -> 修正版

【制御回路用電源設定】

(1)デジタルポテンショメータ(MCP4081)、オペアンプ(NJU7032)の電源電圧は5V

(2)外部に接続するマイコン、およびマイコンとMCP4081間でIICバスにて

通信する電圧は5V

(3)オペアンプの基準電圧は、最大で3V

(4)これらの電子部品が消費電流する電流は、合計しても100mA未満。

以上より、在庫にあったボルテージレギュレータのLM78M05を選定した。

周辺部品として、逆接続防止ダイオード(D1)と 入力電圧<出力電圧 の関係とならない為の

ダイオード(D2)とノイズ対策部品(C1,C2,C3)の配置

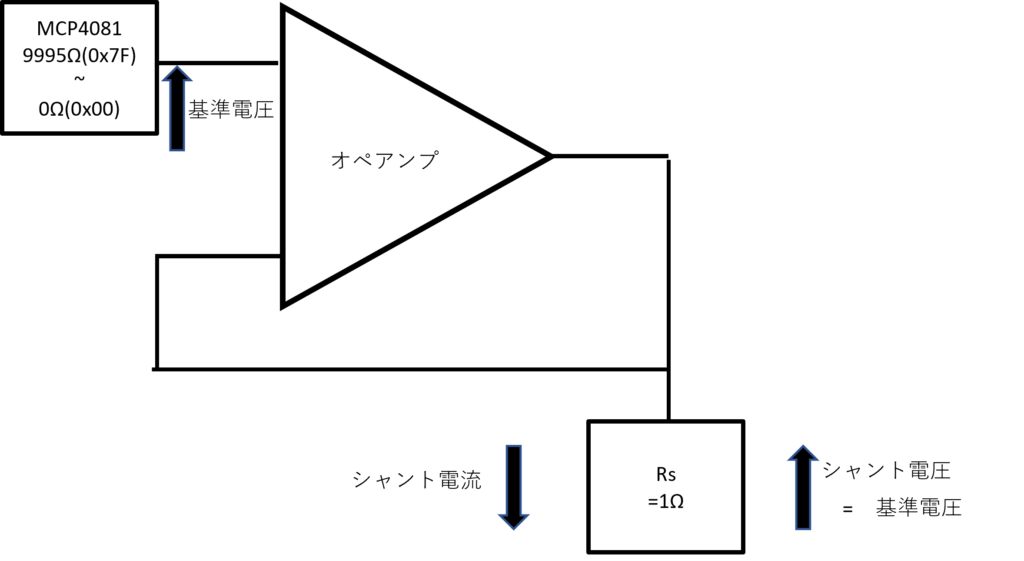

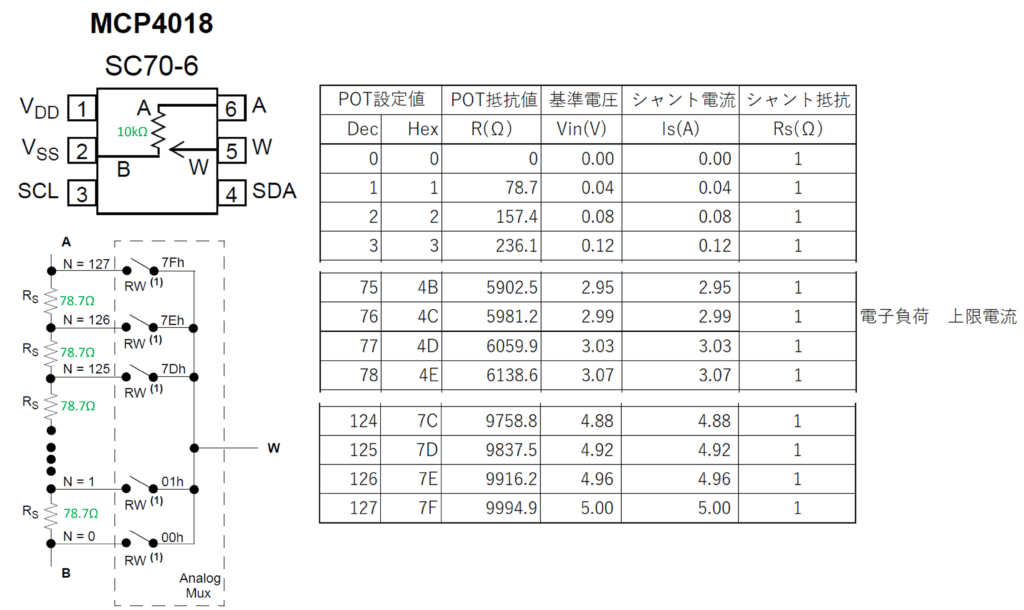

【デジタルポテンショメータ_DigiPOT (MCP4081) 】

<MCP4081特性>

(1)内部抵抗 : 10kΩ

(2)分解能 : 7bit

(3)1ステップ(1hex)当たりの抵抗値 : 78.7Ω (=10kΩ/127)

(4)内部抵抗に流せる電流 : 2.5mA(Max)

<設計>

(1)~(3)より、POT設定値と電流/電圧の関係を Excelで表にした。

その結果、0A~3Aをシャント抵抗に流す場合、

MCP4081の設定値は、00hex~4Chexとなる。

ボルテージレギュレータ出力電圧5VをMCP4081の抵抗端子(A-Vss間)に印加した場合の電流を計算すると、

5V/10kΩ = 0.5mAとなり、(4)の値から、充分定格内であると判断した。

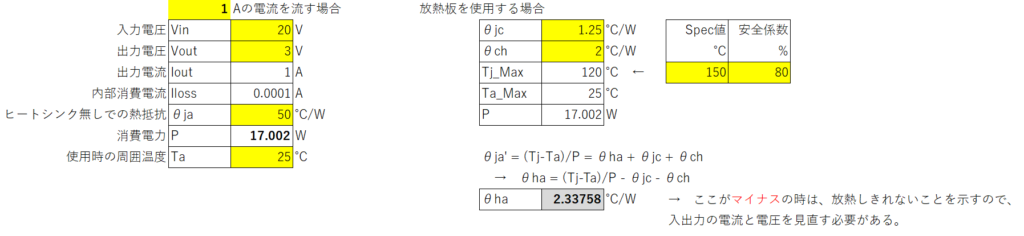

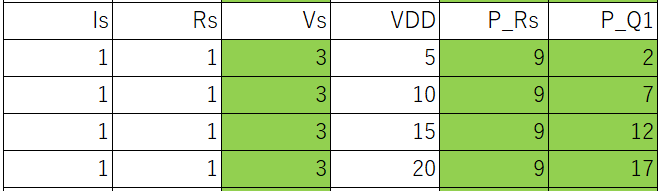

【FET(2SK2232)とシャント抵抗(1Ω)の消費電力(≒放熱量)計算 】

FET1ヶ当たりの消費電力(≒放熱量)を計算

3ヶ合計で3Aの電流を流すので、1ヶ当たり、1Aで計算。

計算は、下表の通り。

シャント抵抗の消費電力(≒放熱量)を計算

これは単純にP=V×Iで計算し、3V×3A で 9W

以上を下表にまとめた。

Is:シャント電流(FET1ヶ当たり)、 Rs:シャント抵抗値、 Vs:シャント電圧

VDD:外部入力電圧、 P_Rs:シャント抵抗で消費する電力、 P_Q1:FET1ヶ当たりの消費電力

念のため検算すると、本電子負荷を最大定格の20V/3Aの設定とした場合、単純に60W(発熱)消費するはず。

一方で下表より、P_Rs + P_Q1×3ヶ = 9W + 17W × 3 = 60W となり、消費電力の計算はあっていそう。

放熱板に対する要求性能は、上記表より 2.33℃/W以下。

【オペアンプの入力抵抗 】

オペアンプは、NJU7032を選定した。

選定理由

(1)電源電圧は、5V単電源で動作可能

(2)基準電圧として最大で3V印加される(+)端子に対し、(-)端子側は、0Vも有り得る

(外部電源未接続など)ので、差動入力電圧範囲が3V以上あること。(*)

(3)0V(直近)まで出力可能なフルスイング品であること。

((*)当初、NJM2732を選択していたが、(2)に気づいて変更した。NJM2732の差動電圧範囲はMax1V)

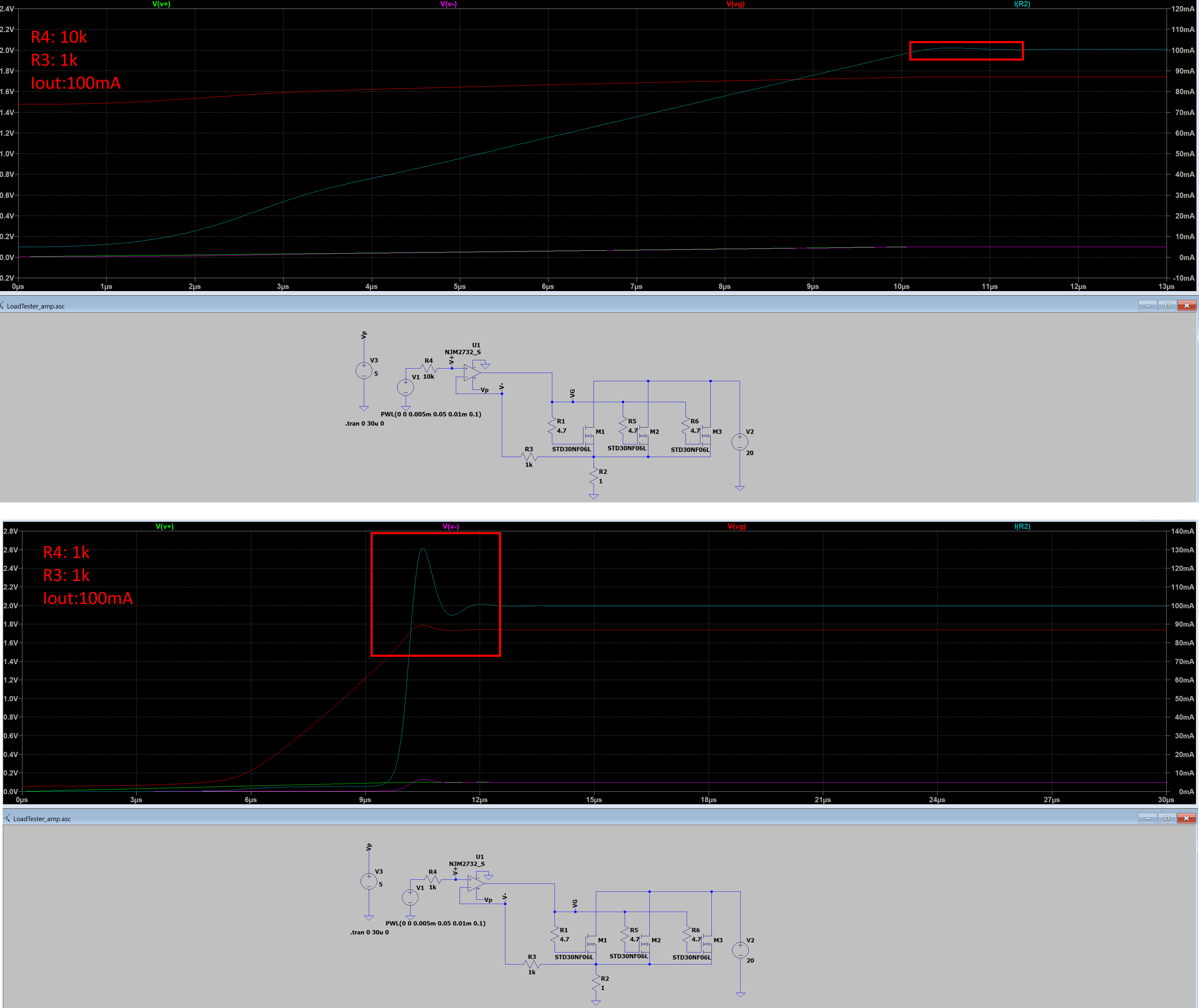

オペアンプの(+)端子と(-)端子に接続する入力抵抗を検討した。

オペアンプの内部回路は、トランジスタで入力を受けている様なので、kΩ台の抵抗で検討してみた。

ざっくり1kΩと10kΩとの場合で、LTspiceで波形確認すると、1kΩ+1kΩの組み合わせの場合、

オーバーシュートが発生するようなので、10kΩ+1kΩの組み合わせを採用した。

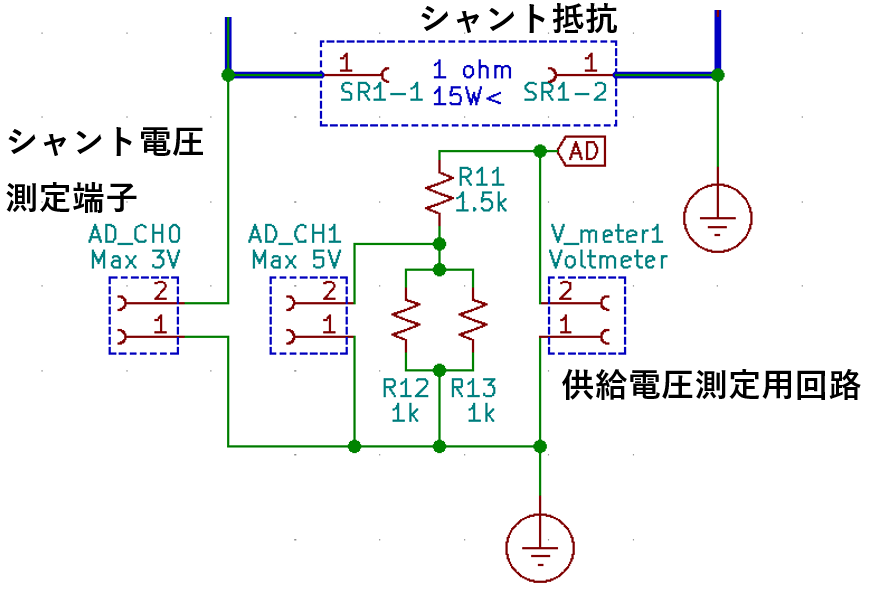

【 測定端子】

下記2点をマイコン(ADポート)で測定できるよう

にした。

(1) シャント抵抗の両端電圧 0V~3V

→ AD_CH0端子へ出力

アプリ処理内で抵抗値(1Ω)で割って、

シャント電流とする。

(2) 外部入力電源 0V~20V

→ 1/4に分圧(0V~5V)して、

AD_CH1端子へ出力

注:抵抗分圧しているだけなので、

入力電圧が20Vをオーバーさせると

マイコンの入力定格も超えてしまう。

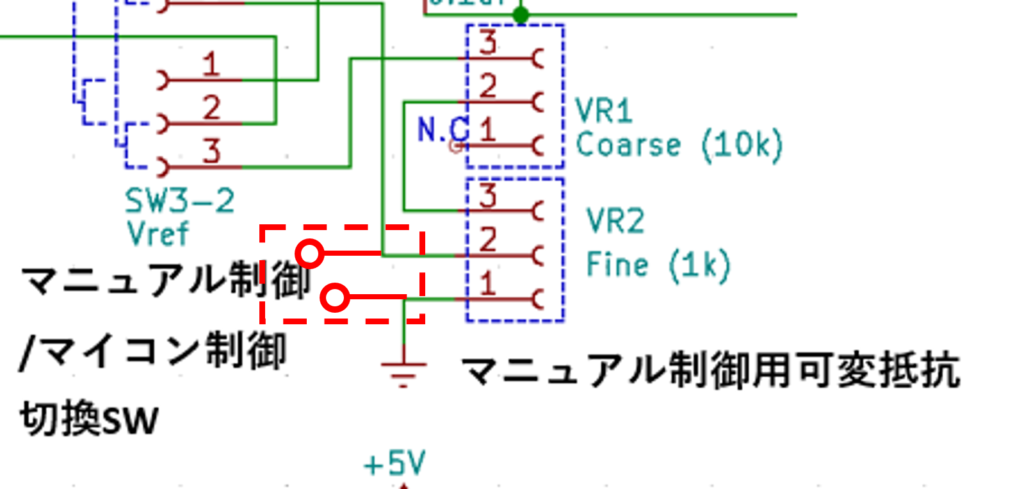

【追記 追加しておけば良かった点】

マニュアル操作でシャント電流を調整する場合、

調整量が分からない。

→ 対策案 基準電圧の測定端子の追加。

【追記 当初の設計から変更した点】

当初FET1ヶで20V、3A定格の電子負荷を設計し、放熱は容量の大きい放熱板を使用すれば何とかなる

と思っていた。

が、60Wの熱(例えば60Wの白熱電球の熱)を本当に冷ませるのか不安になり、放熱計算と放熱設計の

資料の見直しした結果、ダメであると判断した。

(実際に基板作成までしてしまっていた。3000円程度のロス)

<対策>

FET3ヶを並列接続し、電流を3分割することで、FET1ヶ当たりの負担を減らした。

シャント抵抗の値を上げて(0.5Ω→1Ω)、シャント抵抗での負担を上げた。その分FETの負担は更に軽減。

コメント